FWU: Add documentation for Firmware Update feature

This patch adds design documentation for the Firmware Update (FWU)

feature in `firmware-update.md`. It provides an overview of FWU,

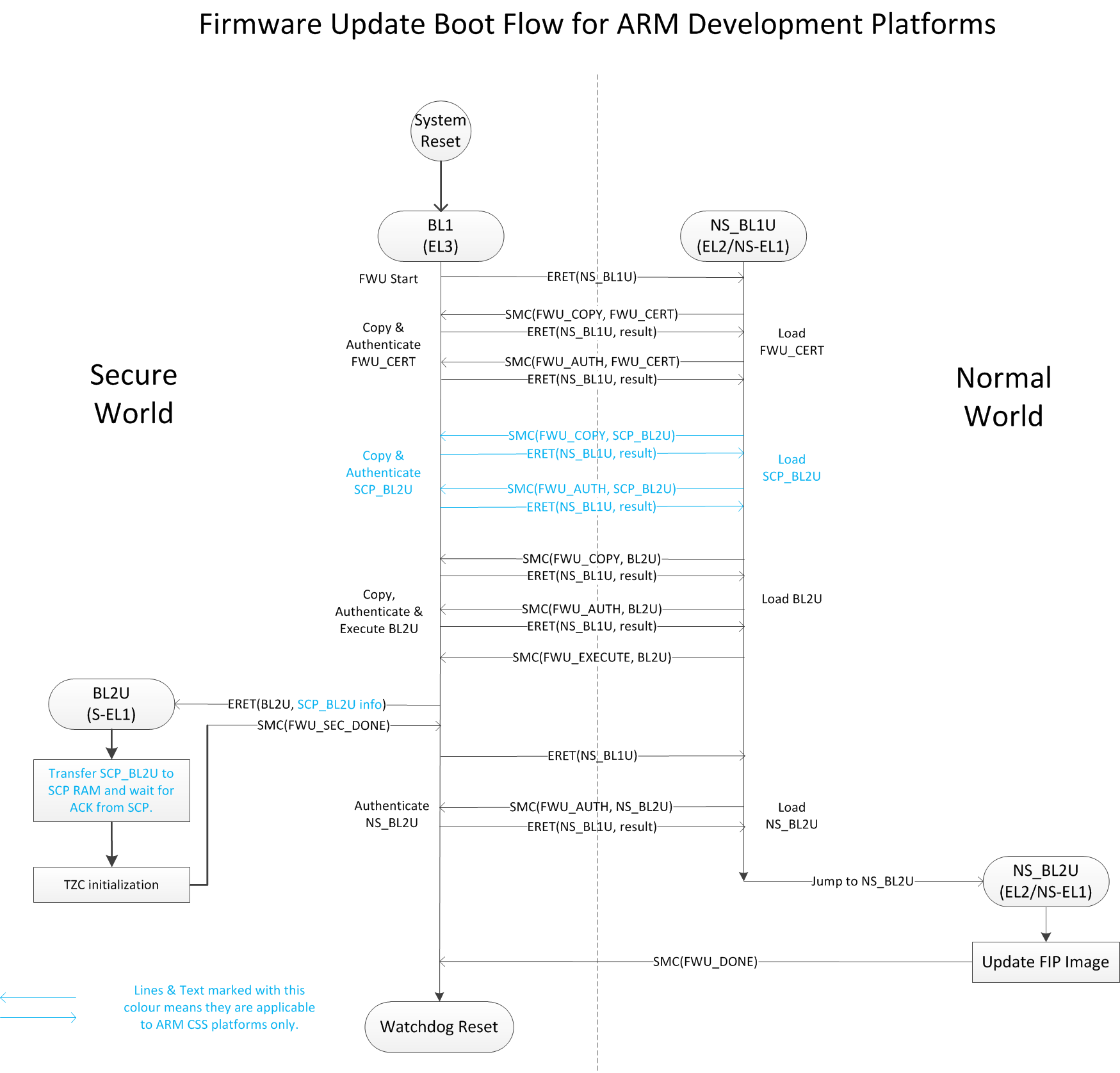

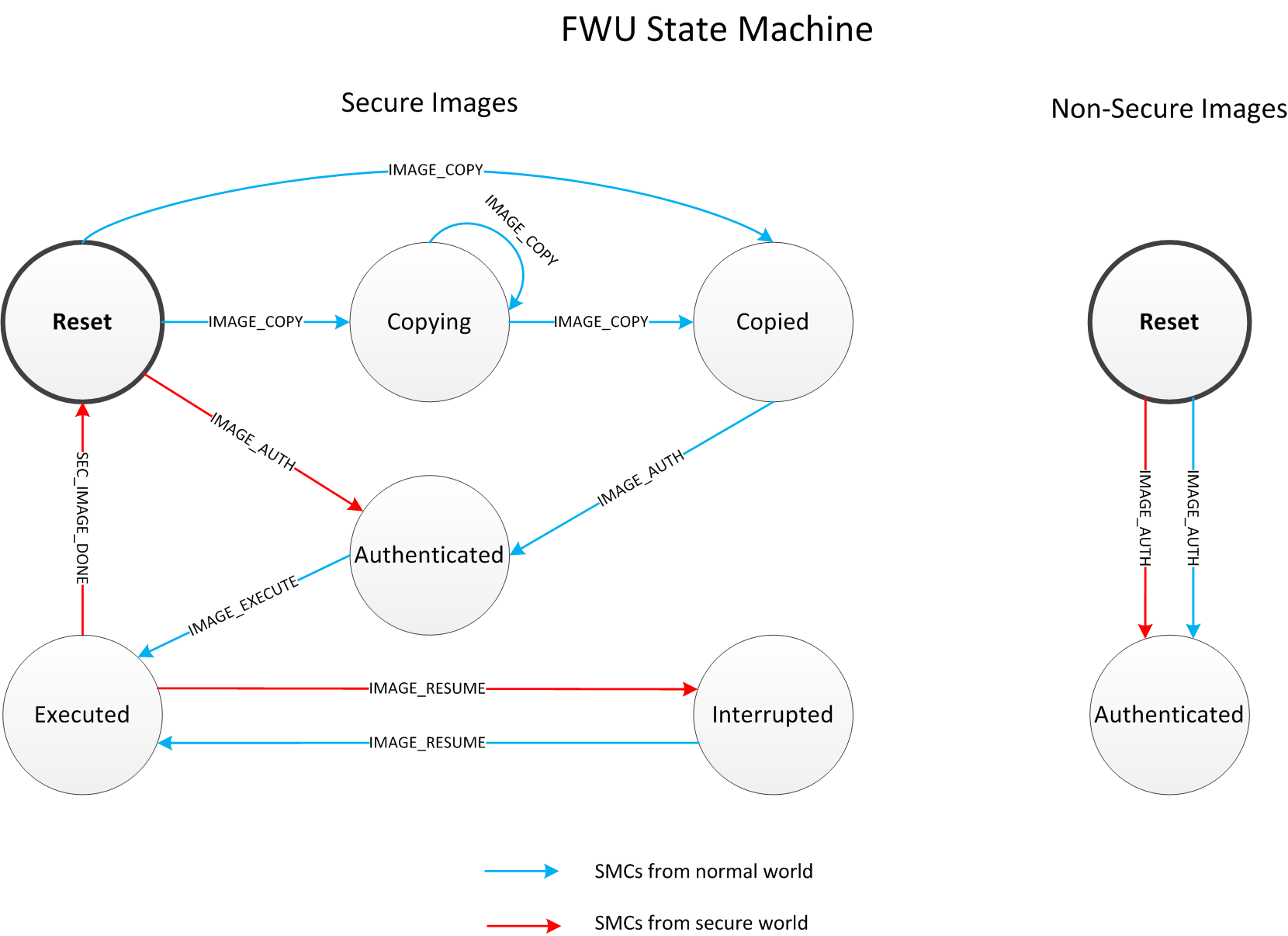

describes the BL1 SMC interface, and includes diagrams showing

an example FWU boot flow and the FWU state machine.

This patch also updates the existing TF documents where needed:

* `porting-guide.md`

* `user-guide.md`

* `firmware-design.md`

* `rt-svc-writers-guide.md`

* `trusted_board_boot.md`

Change-Id: Ie6de31544429b18f01327bd763175e218299a4ce

Co-Authored-By:  Dan Handley <dan.handley@arm.com>

Dan Handley <dan.handley@arm.com>

docs/diagrams/fwu_flow.png

0 → 100644

163 KB

docs/diagrams/fwu_states.png

0 → 100644

112 KB

docs/firmware-update.md

0 → 100644