"plugins/vscode:/vscode.git/clone" did not exist on "13e327eb7c552ded26836247a5f8575dc52e0f6c"

Merge pull request #361 from achingupta/for_sm/psci_proto_v5

For sm/psci proto v5

418 KB

This diff is collapsed.

This diff is collapsed.

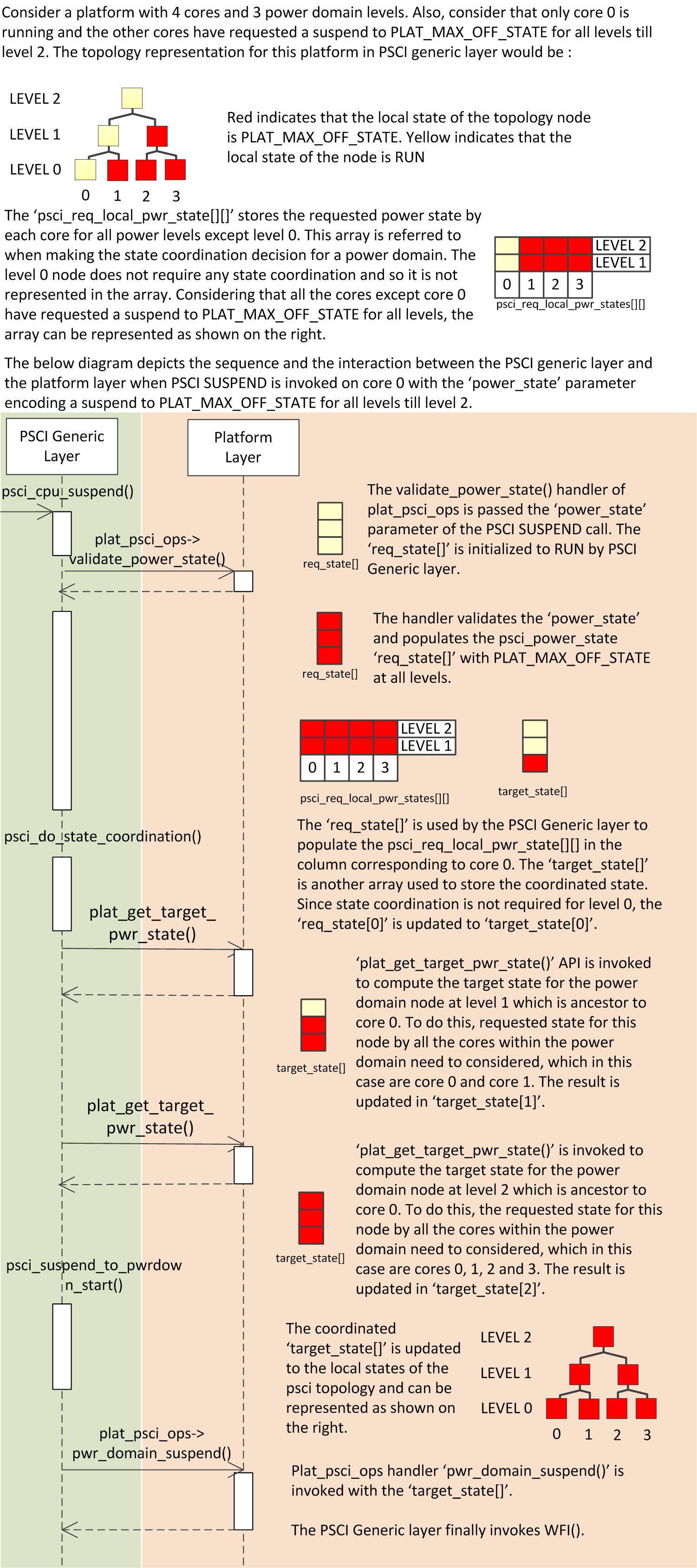

docs/psci-pd-tree.md

0 → 100644