Merge changes from topic "fw-update" into integration

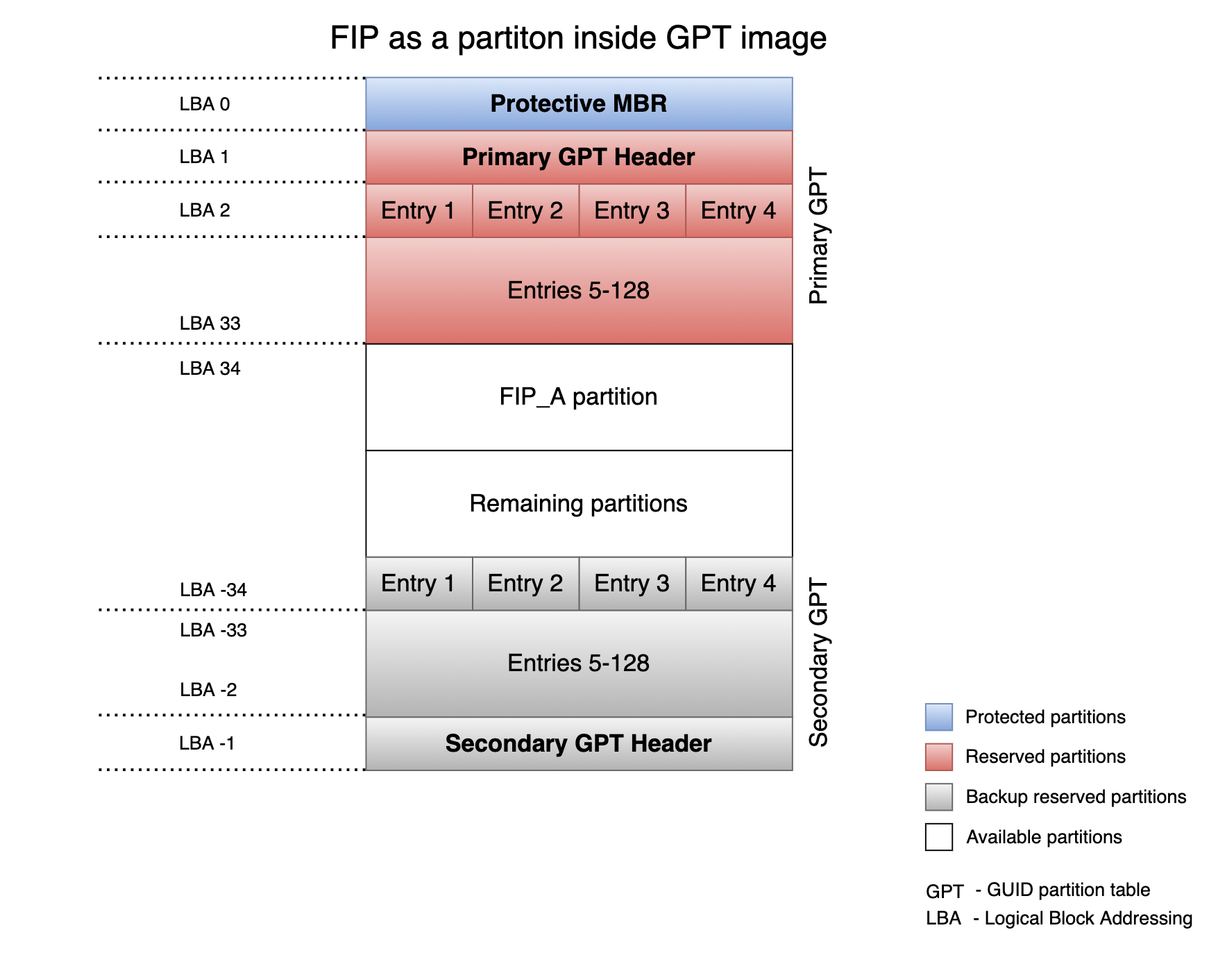

* changes: docs: add build options for GPT support enablement feat(plat/arm): add GPT parser support

244 KB

* changes: docs: add build options for GPT support enablement feat(plat/arm): add GPT parser support

244 KB